Scalable Quantum Error Correction: Breaking Bottlenecks in Quantum Computing

As quantum computing advances toward practical applications, scalable quantum error correction (QEC) has become a pivotal challenge. While improvements in qubit fidelity and coherence times have been significant, achieving fault-tolerant quantum computation requires more than just high-quality qubits. The integration of real-time error detection, decoding, and correction mechanisms is essential to maintain the integrity of quantum information over extended computational processes.

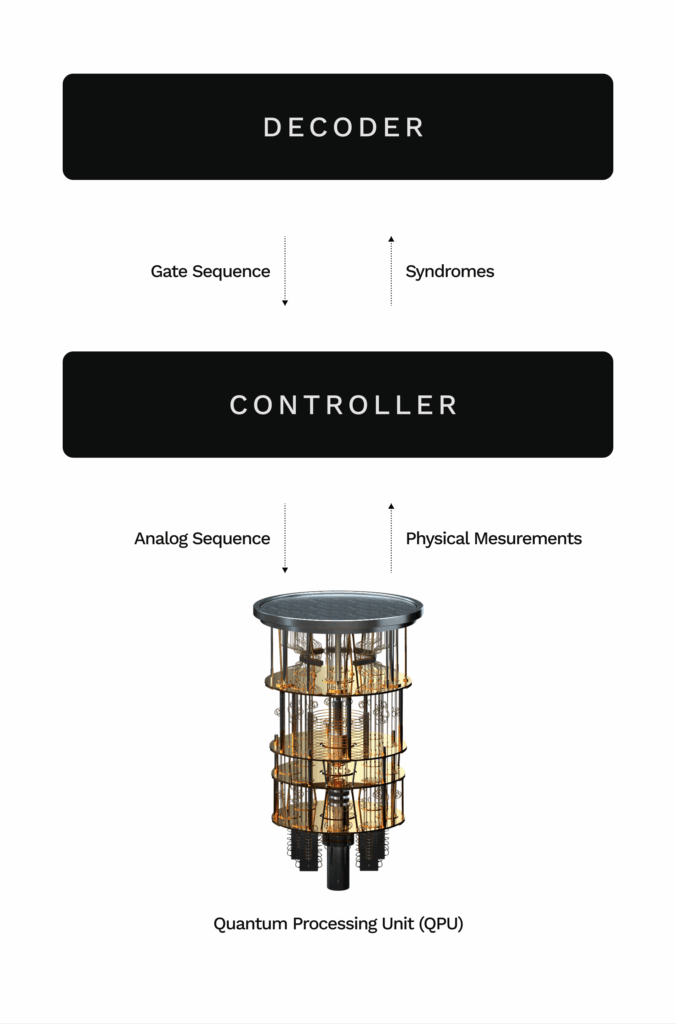

A recent study by Kurman et al. [1] highlights the pressing need for low-latency, tightly integrated controller-decoder systems (CDS). The work demonstrates that the total closed loop latency – from qubit measurement to the application of corrective operations – must remain under a few tens of microseconds for QEC to succeed in realistic non-Clifford quantum circuits. Thus, integration requires bounded latency real-time interconnects. This requirement poses a profound challenge for system architects: to co-design quantum control hardware and classical processing pipelines that can jointly operate under strict timing and synchronization constraints.

Roundtrip data from measurement to correction

Challenges in Scalable Quantum Error Correction

Many leading quantum error correction approaches – including surface codes [2], color codes [3], quantum LDPC codes [4], and emerging dynamic or Floquet codes [5] – rely on frequent stabilizer measurements and fast correction cycles to maintain logical qubit fidelity.

As the number of qubits increases, the overhead grows dramatically – both in terms of physical resources and processing complexity. The CDS must support real-time syndrome extraction, multiple parallel cross-dependent decoding, and feedback across thousands of physical qubits, all while maintaining predictable, bounded latency.

Decoding is not only computationally intensive for large-distance surface codes, but also complex due to the need for cross-dependent parallel decoding. To meet microsecond scale latency constraints, decoding must be distributed across multiple decoders operating in parallel. However, these decoders cannot function independently; due to the nature of logical operations, lattice surgery, and correlated errors across code patches, one decoder may require real-time information from another to make a correct decision. This necessitates inter-decoder communication, dynamic data sharing between decoding processes that cannot be predetermined in their number, structure, or timing. As a result, the controller system must coordinate not only real-time syndrome processing, correction application, and conditional logic, but also a decoding backend capable of flexible, low-latency synchronization across multiple decoding units. The study shows that enabling this adaptive communication is essential to achieving the performance needed for scalable, fault-tolerant quantum computation, and otherwise can lead to a “decoding bottleneck.” This suggests that in addition to the communication latency, the processing capacity and performance of the decoding unit – and the ability to program decoding algorithms efficiently – are also important requirements of the controller decoder architecture.

Industry Approaches

Leading quantum hardware developers and academic institutions have proposed several strategies to meet these demands. Google’s Quantum AI team recently demonstrated fault tolerant logical qubit operation with the Willow processor, showing that logical error rates can be exponentially suppressed below the surface code fault-tolerance threshold [6]. IBM has pursued alternate paths, including research into LDPC codes that aim to reduce overhead while maintaining fault tolerance [7]. Academic groups, including those led by Andreas Wallraff (ETH Zurich) and Leo DiCarlo (TU Delft), are also advancing the field through research on lattice surgery, scalable QEC integration, and improved decoder architectures [8,9].

Latencies introduced by different data transfer interfaces and protocols can make some architectures impractical for large-scale QEC unless tightly coupled with the control system. The quantum controller must also track qubit frequencies in real time and dynamically retune control pulses to compensate for frequency drifts during computation. This ongoing tuning – sometimes referred to as real-time calibration or intra-circuit recalibration – is critical for keeping physical error rates below the threshold required by the QEC code. If left unaddressed, such drifts can degrade the fidelity of QEC operations and cause error correction to fail.

Quantum Machines’ Hybrid Control Solution

Quantum Machines addresses these system-level challenges through its Hybrid Control approach, building upon its core control solution, OPX1000. The OPX1000 controller is a modular, high-density quantum control platform built around the Pulse Processing Unit (PPU) – Quantum Machines’ unique real-time processor designed specifically for scalable quantum control that combines real-time classical operations – including computations and control flow – with quantum control at the pulse level. Each front-end module (FEM) in OPX1000 – whether low-frequency (LF-FEM) or microwave (MW-FEM) – includes a dedicated PPU. All PPUs in an OPX1000 cluster are programmed and operated together as one unified control system. They handle pulse generation, measurement, and ultra-fast real-time processing, while managing synchronization and data sharing across the system. This Hybrid Control architecture brings classical operations as close as possible to the qubits; thus minimizing latencies, and optimizing performance across software and hardware layers of the quantum computer.

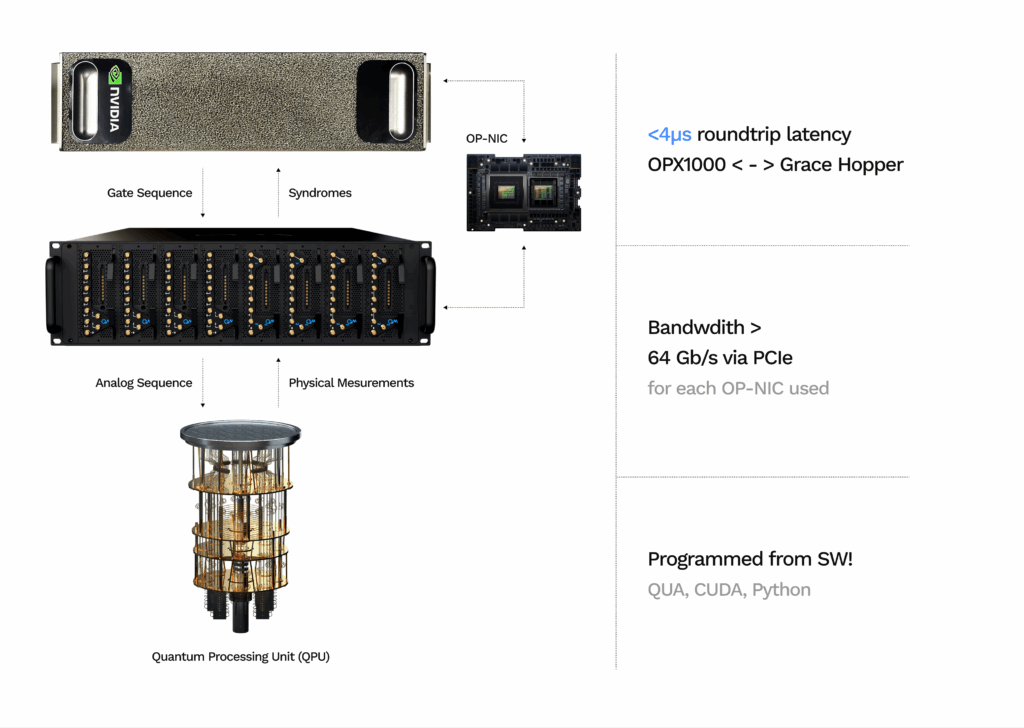

But the low latencies required for real-time decoding at scale are not handled solely by the controller. To achieve that, Quantum Machines and NVIDIA co-developed DGX Quantum [6]. This system directly connects the PPUs to high-performance GPU and CPU accelerators via a high-bandwidth, low-latency optical network interface card (OP-NIC). Quantum Machines’ OP-NIC acts as real-time interconnect, offering bounded-latency integration between the quantum system controller and the CPU/GPU server. With a roundtrip latency below 4 µs, DGX Quantum delivers unmatched speed – over 1,000x faster than other solutions – allowing externally executed decoding routines, including classical and machine-learning-based algorithms, to participate in QEC cycles without breaking timing constraints. Importantly, using a high-performance computational resource such as NVIDIA’s Grace Hopper superchip allows the implementation of efficient cross-dependent parallel decoding, with the flexibility of software programming.

Considering scalability – DGX Quantum is scalable in two directions: more OPX1000 controllers can be added for a larger QPU, and more Grace Hopper servers can be added for

increasing classical compute needs.

NVIDIA DGX Quantum – the first integrated CPU-GPU-QPU system

The solution includes a rich software package, from pulse-level programming in QUA to integration with CUDA-Q, enabling the efficient development of classical and quantum hybrid workflows that combine pulse-level control with accelerated classical computation in a unified execution model. This single programming interface further enables DGX Quantum’s compatibility with NVQLink, NVIDIA open architecture for hybrid quantum-classical computing.

The resulting architecture allows QEC protocols to be implemented and iterated at scale, without requiring extensive customization or hardcoded firmware. Researchers gain the flexibility to evaluate and deploy different decoding strategies and code constructions while relying on the same underlying stack for real-time execution.

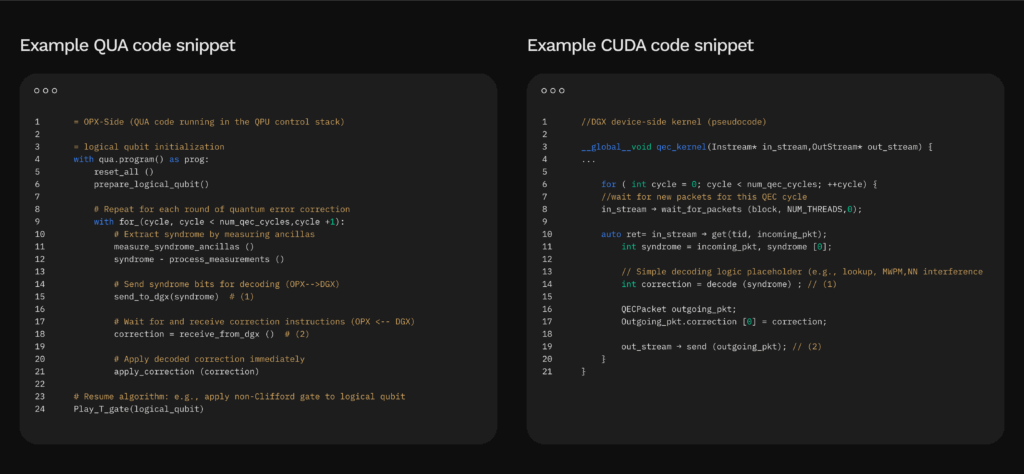

To better understand this, let’s have a look at QUA and QUDA code snippets that demonstrate the simple data transmission interface between OPX and GPU acceleration via the DGX Quantum solution.

Conclusion

As quantum systems scale beyond the NISQ regime, the need for robust and real-time quantum error correction becomes mandatory. Control latency, decoding throughput, and synchronization are no longer implementation details – they define the boundary between experimental devices and practical fault-tolerant quantum computers.

Quantum Machines’ Hybrid Control architecture, centered around OPX1000 and powered by its PPU, can uniquely integrated with external accelerators via DGX Quantum – providing a scalable, deterministic platform for advancing QEC. It removes bottlenecks in the controller-decoder interface and provides the flexibility needed to support evolving QEC research and system design. With this foundation, researchers and quantum computer builders can take meaningful steps toward fault-tolerant architectures and, ultimately, practical commercial quantum supercomputers.

Ready to accelerate your quantum error correction research? Explore how NVIDIA DGX Quantum can empower your experiments.

References

[1] Y. Kurman et al., Controller-decoder requirements for the next-gen of quantum error correction circuits, arXiv:2412.00289 (2024).

[2] A. Bapat et al., Syndrome extraction for fault-tolerant quantum computing with long ion chains, arXiv:2503.22071 (2025).

[3] A. Bačkurs and N. Delfosse, Minimizing surface code failures using color code decoders, Quantum 9, 1632 (2025).

[4] M. V. Sivak et al., Universal fault-tolerant quantum computing with LDPC codes and cat qubits, Nature Communications 15, 2146 (2025).

[5] M. P. Woods et al., Floquet codes without parent subsystem codes, PRX Quantum 5, 020305 (2024).

[6] Google Quantum AI, Quantum error correction below the surface code threshold, Nature (2024).

[7] IBM Research, Quantum Error Correction Overview, https://research.ibm.com/topics/quantum-error-correction

[8] ETH Zurich (A. Wallraff Group), https://www.qudev.ethz.ch

[9] TU Delft (L. DiCarlo Group), https://dicarlo.tudelft.nl